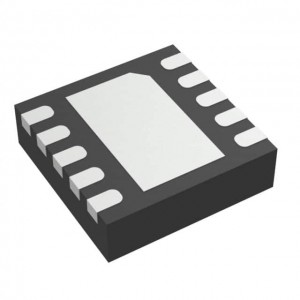

Мікракантролер Semicon Рэгулятар напружання IC Chips TPS62420DRCR SON10 Электронныя кампаненты Спіс спісаў BOM

Атрыбуты прадукту

| ТЫП | АПІСАННЕ |

| Катэгорыя | Інтэгральныя схемы (ІС) Рэгулятары напружання - DC Імпульсныя рэгулятары пастаяннага току |

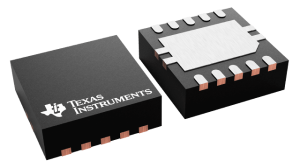

| Вытворца | Texas Instruments |

| серыял | - |

| Пакет | Стужка і шпулька (TR) Абрэзаная стужка (CT) Digi-Reel® |

| SPQ | 3000T&R |

| Статус прадукту | Актыўны |

| Функцыя | Прыступка ўніз |

| Канфігурацыя вываду | Пазітыўны |

| Тапалогія | Бак |

| Тып вываду | Рэгуляваны |

| Колькасць выхадаў | 2 |

| Уваходнае напружанне (мінімум) | 2,5 В |

| Напружанне - Уваход (макс.) | 6V |

| Напружанне - выхад (мінімум/фіксаваны) | 0,6 В |

| Напружанне - выхад (макс.) | 6V |

| Ток - выхад | 600 мА, 1 А |

| Частата - пераключэнне | 2,25 МГц |

| Сінхронны выпрамнік | так |

| Працоўная тэмпература | -40°C ~ 85°C (TA) |

| Тып мацавання | Павярхоўны мантаж |

| Пакет / Чахол | 10-VFDFN адкрытая накладка |

| Пакет прылады пастаўшчыка | 10-VSON (3x3) |

| Базавы нумар прадукту | TPS62420 |

Канцэпцыя ўпакоўкі:

Вузкі сэнс: працэс размяшчэння, мацавання і злучэння чыпаў і іншых элементаў на раме або падкладцы з выкарыстаннем плёнкавых тэхналогій і метадаў мікрафабрыкацыі, які вядзе да клем і фіксуе іх шляхам залівання падатлівым ізаляцыйным асяроддзем для фарміравання агульнай трохмернай структуры.

Шырока кажучы: працэс злучэння і замацавання ўпакоўкі на падкладцы, зборкі яе ў поўную сістэму або электронную прыладу і забеспячэнне поўнай прадукцыйнасці ўсёй сістэмы.

Функцыі, якія выконваюцца ўпакоўкай мікрасхем.

1. які перадае функцыі;2. перадачы сігналаў схемы;3. забеспячэнне сродкаў адводу цяпла;4. структурная абарона і падтрымка.

Тэхнічны ўзровень упаковачнай тэхнікі.

Распрацоўка ўпакоўкі пачынаецца пасля вырабу мікрасхемы і ўключае ў сябе ўсе працэсы перад тым, як мікрасхема ўклейваецца і фіксуецца, злучаецца паміж сабой, герметызуецца, герметызуецца і абараняецца, падключаецца да друкаванай платы і збіраецца сістэма, пакуль не будзе завершаны канчатковы прадукт.

Першы ўзровень: таксама вядомы як упакоўка на ўзроўні чыпа, - гэта працэс мацавання, злучэння і абароны чыпа IC на ўпаковачнай падкладцы або рамцы, што робіць яго кампанентам модуля (зборкі), які можна лёгка браць, транспартаваць і злучаць на наступны ўзровень зборкі.

Узровень 2: Працэс аб'яднання некалькіх пакетаў з узроўню 1 з іншымі электроннымі кампанентамі для фарміравання схемнай карты.Узровень 3: Працэс аб'яднання некалькіх схемных карт, сабраных з пакетаў, завершаных на ўзроўні 2, для фарміравання кампанента або падсістэмы на галоўнай плаце.

Узровень 4: Працэс зборкі некалькіх падсістэм у поўны электронны прадукт.

У чыпе.Працэс злучэння кампанентаў інтэгральнай схемы на мікрасхеме таксама вядомы як упакоўка нулявога ўзроўню, таму ўпаковачную тэхніку таксама можна падзяліць на пяць узроўняў.

Класіфікацыя пакетаў:

1, у залежнасці ад колькасці чыпаў IC у ўпакоўцы: упакоўка з адным чыпам (SCP) і ўпакоўка з некалькімі чыпамі (MCP).

2, у залежнасці ад адрозненні матэрыялу ўшчыльнення: палімерныя матэрыялы (пластык) і кераміка.

3, у залежнасці ад рэжыму злучэння прылады і друкаванай платы: тып устаўкі штыфта (PTH) і тып павярхоўнага мантажу (SMT) 4, у адпаведнасці з формай размеркавання штыфта: аднабаковыя штыфты, двухбаковыя шпількі, чатырохбаковыя штыфты і ніжнія шпількі.

Прылады SMT маюць металічныя штыфты L-тыпу, J-тыпу і I-тыпу.

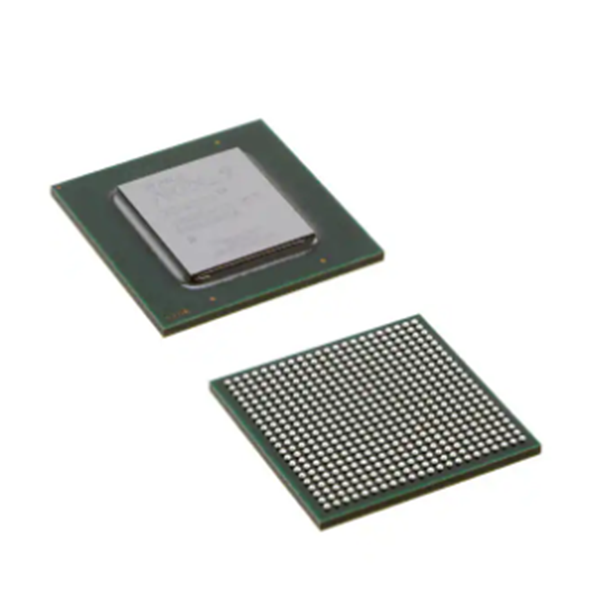

SIP: аднарадковая ўпакоўка SQP: мініяцюрная ўпакоўка MCP: металічная ўпакоўка DIP: двухрадковая ўпакоўка CSP: упакоўка памеру мікрасхемы QFP: чатырохбаковая плоская ўпакоўка PGA: матрычная ўпакоўка BGA: упакоўка з шарыкавай сеткай LCCC: бессвінцовы керамічны носьбіт чыпаў