Электронныя мікрасхемы Падтрымка BOM Service TPS54560BDDAR абсалютна новыя мікрасхемы электронныя кампаненты

Атрыбуты прадукту

| ТЫП | АПІСАННЕ |

| Катэгорыя | Інтэгральныя схемы (ІС) Рэгулятары напружання - DC Імпульсныя рэгулятары пастаяннага току |

| Вытворца | Texas Instruments |

| серыял | Eco-Mode™ |

| Пакет | Стужка і шпулька (TR) Абрэзаная стужка (CT) Digi-Reel® |

| SPQ | 2500T&R |

| Статус прадукту | Актыўны |

| Функцыя | Прыступка ўніз |

| Канфігурацыя вываду | Пазітыўны |

| Тапалогія | Бак, Split Rail |

| Тып вываду | Рэгуляваны |

| Колькасць выхадаў | 1 |

| Уваходнае напружанне (мінімум) | 4,5 В |

| Напружанне - Уваход (макс.) | 60В |

| Напружанне - выхад (мінімум/фіксаваны) | 0,8 В |

| Напружанне - выхад (макс.) | 58,8 В |

| Ток - выхад | 5A |

| Частата - пераключэнне | 500 кГц |

| Сінхронны выпрамнік | No |

| Працоўная тэмпература | -40°C ~ 150°C (TJ) |

| Тып мацавання | Павярхоўны мантаж |

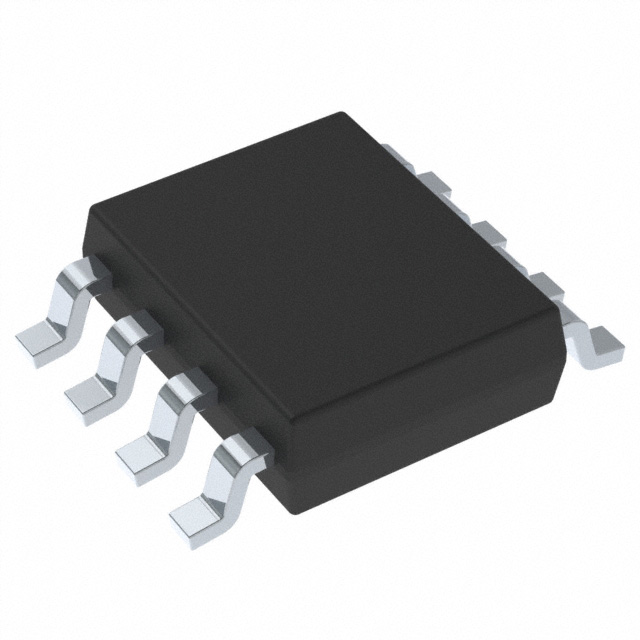

| Пакет / Чахол | 8-PowerSOIC (0,154 цалі, шырыня 3,90 мм) |

| Пакет прылады пастаўшчыка | 8-SO PowerPad |

| Базавы нумар прадукту | TPS54560 |

1.Назвы IC, агульныя веды пакетаў і правілы наймення:

Дыяпазон тэмператур.

C=0°C да 60°C (таварны гатунак);I=-20°C да 85°C (прамысловы клас);E=-40°C да 85°C (пашыраны прамысловы клас);A=-40°C да 82°C (аэракасмічны клас);M=-55°C да 125°C (ваенны клас)

Тып пакета.

A-SSOP;B-CERQUAD;C-TO-200, TQFP;D-керамічная медная верхняя частка;E-QSOP;F-кераміка SOP;H- SBGAJ-керамічны DIP;К-ТО-3;L-LCC, M-MQFP;N-вузкі DIP;N-DIP;Q PLCC;R - Вузкая кераміка DIP (300mil);S - ТО-52, Т - ТО5, ТО-99, ТО-100;U - TSSOP, uMAX, SOT;W - Wide Small Form Factor (300 mil) W-Wide Small Form Factor (300 mil);X-SC-60 (3P, 5P, 6P);Y-вузкі медны верх;Z-TO-92, MQUAD;D-Die;/PR-армаваны пластык;/W-вафля.

Колькасць шпілек:

а-8;б-10;з-12, 192;д-14;е-16;ф-22, 256;г-4;ч-4;i -4;Н-4;І-28;J-2;К-5, 68;Л-40;М-6, 48;N 18;О-42;П-20;Q-2, 100;Р-3, 843;С-4, 80;Т-6, 160;У-60 -6 160;У-60;V-8 (круглы);Ш-10 (круглы);Х-36;Y-8 (круглы);Z-10 (круглы).(круглы).

Заўвага: першая літара чатырохлітарнага суфікса класа інтэрфейсу - E, што азначае, што прылада мае антыстатычную функцыю.

2.Распрацоўка тэхналогіі ўпакоўкі

Самыя раннія інтэгральныя схемы выкарыстоўвалі керамічныя плоскія пакеты, якія працягвалі выкарыстоўвацца ў вайскоўцах на працягу многіх гадоў з-за іх надзейнасці і невялікіх памераў.Камерцыйная ўпакоўка схем неўзабаве перайшла на корпусы з падвойнай лініяй, пачынаючы з керамікі, а затым з пластыка, і ў 1980-х гадах колькасць кантактаў у схемах VLSI перавысіла абмежаванні прымянення пакетаў DIP, што ў канчатковым выніку прывяло да з'яўлення масіваў кантактнай сеткі і носьбітаў мікрасхем.

Пакет для павярхоўнага мантажу з'явіўся ў пачатку 1980-х гадоў і стаў папулярным у канцы гэтага дзесяцігоддзя.Ён мае больш дробны крок шпілек і мае форму крыла чайкі або J-вобразную форму.Напрыклад, інтэгральная схема малога контуру (SOIC) мае на 30-50% меншую плошчу і на 70% меншую таўшчыню, чым эквівалентная DIP.Гэты пакет мае штыфты ў форме крыла чайкі, якія выступаюць з двух доўгіх бакоў, і крок шпілек складае 0,05 цалі.

Пакеты інтэгральных схем малога памеру (SOIC) і PLCC.у 1990-я гады, хоць пакет PGA па-ранейшаму часта выкарыстоўваўся для мікрапрацэсараў высокага класа.PQFP і тонкі пакет малога контуру (TSOP) сталі звычайным пакетам для прылад з вялікай колькасцю кантактаў.Высокакласныя мікрапрацэсары Intel і AMD перайшлі з пакетаў PGA (Pine Grid Array) на пакеты Land Grid Array (LGA).

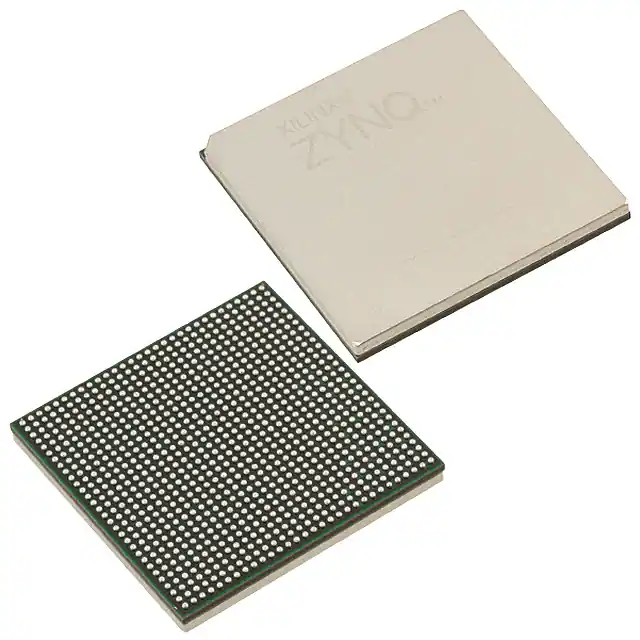

Пакеты Ball Grid Array пачалі з'яўляцца ў 1970-х гадах, а ў 1990-х гадах быў распрацаваны пакет FCBGA з большай колькасцю кантактаў, чым іншыя пакеты.У корпусе FCBGA плашка перагортваецца ўверх і ўніз і злучаецца з шарыкамі прыпоя на ўпакоўцы базавым пластом, падобным на друкаваную плату, а не правадамі.На сучасным рынку ўпакоўка таксама з'яўляецца асобнай часткай працэсу, і тэхналогія ўпакоўкі таксама можа паўплываць на якасць і выхад прадукту.