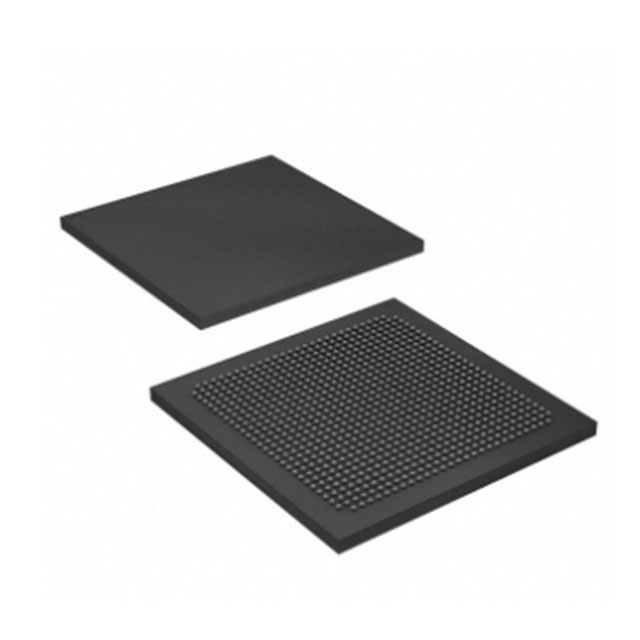

5CEFA5F23I7N Cyclone® VE Праграмуемая вентыльная матрыца (FPGA) IC 240 5001216 77000 484-BGA

Атрыбуты прадукту

| ТЫП | ІЛЮСТРАВАЦЬ |

| катэгорыя | Праграмуемыя вентыльныя масівы (FPGA) |

| вытворца | Intel |

| серыял | Cyclone® VE |

| абгарнуць | латок |

| Статус прадукту | Актыўны |

| DigiKey праграмуецца | Не правераны |

| Нумар LAB/CLB | 29080 |

| Колькасць лагічных элементаў/адзінак | 77000 |

| Агульная колькасць біт аператыўнай памяці | 5001216 |

| Увод-вывад 數 | 240 |

| Напружанне - крыніца харчавання | 1,07 В~1,13 В |

| Тып ўстаноўкі | Тып клею для паверхні |

| Працоўная тэмпература | -40°C ~ 100°C (TJ) |

| Пакет/корпус | 484-БГА |

| Інкапсуляцыя кампанента пастаўшчыка | 484-FBGA (23x23) |

| Галоўны нумар прадукту | 5CEFA5 |

Увядзенне прадукту

Прылады Cyclone® V распрацаваны з улікам зніжэння энергаспажывання, кошту і часу выхаду на рынак;і павелічэнне патрабаванняў да прапускной здольнасці для вялікіх аб'ёмаў і недарагіх прыкладанняў.Палепшаныя інтэграванымі прыёмаперадатчыкамі і жорсткімі кантролерамі памяці, прылады Cyclone V падыходзяць для прымянення ў прамысловых, бесправадных і правадных, ваенных і аўтамабільных рынках.

Асаблівасці прадукту

Тэхналогіі

- Тэхпрацэс 28-нм з нізкім энергаспажываннем (28LP) TSMC

- Напружанне ядра 1,1 В

Ўпакоўка

- Пакеты Wirebond з нізкім утрыманнем галагенаў

- Некалькі шчыльнасцей прылад з сумяшчальнымі адбіткамі пакетаў для плаўнай міграцыі паміж рознымі шчыльнасцямі прылад

- Сумяшчальныя з RoHS і этыляваныя варыянты

Высокапрадукцыйная тканіна FPGA

- Палепшаны ALM з 8 уваходамі і чатырма рэгістрамі

Блокі ўнутранай памяці

- M10K—блокі памяці па 10 кілабіт (Кб) з праграмным кодам выпраўлення памылак (ECC)

- Блок лагічнага масіва памяці (MLAB) — 640-бітны размеркаваны LUTRAM, дзе вы можаце выкарыстоўваць да 25% ALM у якасці памяці MLAB

Убудаваныя жорсткія блокі IP

- Уласная падтрымка да трох узроўняў дакладнасці апрацоўкі сігналу (тры 9 х 9, два 18 х 18 або адзін 27 х 27 множнік) у адным блоку DSP з пераменнай дакладнасцю

- 64-бітны акумулятар і каскад

- Убудаваная ўнутраная памяць каэфіцыентаў

- Папярэдні суматар/аднімач для павышэння эфектыўнасці

- DDR3, DDR2 і LPDDR2 з падтрымкай 16 і 32 біт ECC

- Жорсткі IP PCI Express* (PCIe*) Gen2 і Gen1 (x1, x2 або x4) з шматфункцыянальнай падтрымкай, канчатковай кропкай і каранёвым портам

Канфігурацыя

- амперная абарона—комплексная абарона дызайну для абароны вашых каштоўных інвестыцый у IP

- Палепшаныя функцыі бяспекі распрацоўкі пашыранага стандарту шыфравання (AES).

- CvP

- Дынамічная рэканфігурацыя FPGA

- Параметры канфігурацыі актыўнага паслядоўнага (AS) x1 і x4, пасіўнага паслядоўнага (PS), JTAG і хуткага пасіўнага паралельнага (FPP) x8 і x16

- Унутраная чыстка (2)

- Частковая рэканфігурацыя (3)

Напішыце тут сваё паведамленне і адпраўце яго нам